Автор разработки: А.Грицаенко

Схема принципиальная Четырехвходовый логический анализатор

Очень часто при ремонте электронных узлов на базе цифровых микросхем малой и средней степени интеграции возникают вопросы выяснения реализуемой функции, в зависимости от той или иной комбинации входных сигналов. Как правило, основные затруднения при "вычислении" неисправного элемента вызывает статическое состояние схемы или части схемы, в результате чего при сравнении предполагаемого значения логической функции и ее фактического значения возможны ошибки. То есть при определенной комбинации входных сигналов схема может находиться в таком состоянии, которое даст ложную информацию об исправности используемых в ней элементов.

Предлагаемый четырехвходовый логический анализатор позволяет визуально отобразить действительно реализуемое в "динамике" состояние схемы или ее части в виде карты Карно с последующим сравнением реальных значений функции с вычисленными. Анализатор также можно использовать для перевода схемы на другую элементную базу, что немаловажно для радиолюбителей, живущих на периферии и часто сталкивающихся с проблемой замены какой-либо микросхемы.

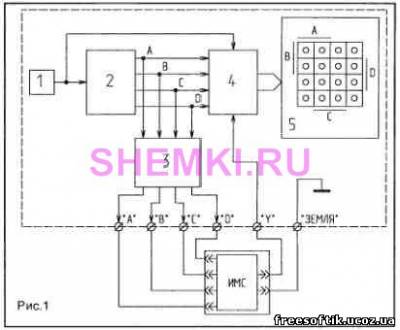

Структурная схема анализатора представлена на рис.1.

Анализатор состоит из следующих блоков:

1 — задающий генератор;

2 — четырехразрядный двоичный счетчик, реализующий 16 комбинаций из переменных А, В, С, D;

3 — буферный усилитель сигналов, подаваемых на исследуемую микросхему (ИМС);

4 — блок памяти;

5 — блок отображения.

Задающий генератор 1 совместно с счетчиком 2 выдает периодическую последовательность, состоящую из 16 наборов двоичных сигналов А, В, С, D. В определенный момент времени один из наборов подастся на входы исследуемой ИМС, а реакция схемы фиксируется в блоке памяти 4, содержимое которого выводится в блок отображения 5. Данные блока памяти обновляются с частотой, равной 1/16 частоты генератора. Таким образом, по "световой картинке" можно судить о реально реализуемой функции ИМС.

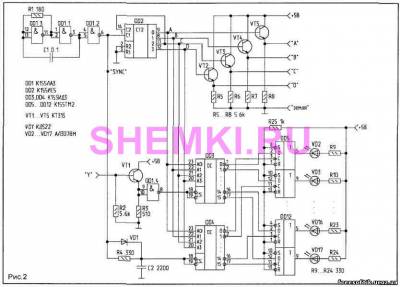

Принципиальная схема устройства показана на рис.2.

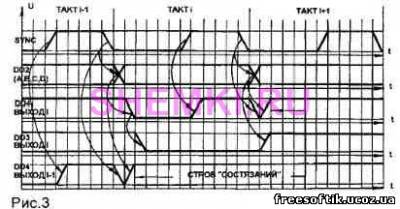

Тактовая последовательность генератора, собранного па элементах DD1.1...D1.3, поступает на вход двоичного счетчика DD2, на выходах которого получаем комбинации из сигналов А, В, С, D. Каждая из комбинации подается па входы исследуемой схемы через блок усилителей, представляющих собой эмиттерные повторители, собранные на VT2...VT5. Одновременно сигналы от счетчика поступают на входы блока памяти, выполненного на микросхемах DD3...DD12. Сигнал результирующей функции от ИМС через согласующее устройство (R2, VT1, R3, DD1.4) подается на информационный вход ОЭЗ и далее — на информационный вход соответствующего триггера, в зависимости от двоичной комбинации А, В, С, D. Запись значения функции в триггер осуществляется по переднему фронту сигнала синхронизации SYNC, поступающего на синхровход соответствующего триггера через DD4. Процесс записи единичного значения функции в i-й триггер показан на рис.3.

На элементах VD1, R4 и С2 собрана цепь задержки заднего фронта сигнала SYNC для исключения возможности появления на предыдущем (i-й) выходе DD4 строба "состязаний" (рис.3). Параметры цепочки рассчитываются исходя из условия: t задержки должно быть больше суммарного времени переключения DD2 и времени установления сигналов на входах DD4.

Частоту задающего генератора следует выбирать так, чтобы не возникало проблем при расчете параметров элементов задержки, но чтобы не наблюдалось мерцания светодиодов при низкой частоте.

Блок отображения представляет собой набор светодиодов, расположенных на печатной плате в виде матрицы 4x4 и выведенных на лицевую панель прибора. На панели изображена карта Карно, где каждой ее клетке соответствует определенный светодиод.

В качестве элементной базы анализатора использовались микросхемы серии К155, которые могут быть заменены на соответствующие ТТЛ-серий (К555, К1533,...).

Транзисторы VT1...VT5 — типа КТ315 с любым буквенным индексом. Диод VD1 — кремниевый типа КД522. Светодиоды VD2...VD17 — АЛ307БМ.

Конденсаторы С1 и С2 — любые малогабаритные, бумажные или металлокерамические.

На лицевую панель анализатора выведены 6 одноштырьковых разъемов: 4 — для коммутации выходных сигналов прибора и входов исследуемой ИМС, один — для подключения результирующей функции, и еще один — для соединения корпусов ("земли") ИМС и анализатора.

Конечно, предлагаемый анализатор содержит ряд недостатков, один из которых заключается в необходимости отключения внешних сигналов от исследуемой ИМС или ее части, а значит, иногда приходится перерезать токопроводящие дорожки печатной платы. Но, как говорится, за все нужно платить: простота прибора, компактность, удобство в использовании, высокая надежность результатов анализа позволяют довольно быстро обнаружить неисправные микросхемы.

Источник: А.Грицаенко, журнал "Радиолюбитель". Схемы и статьи публикуются с разрешения редакции журнала.

Похожие материалы:

К сожалению, похожего ничего не нашлось!

|