11:10 Экономичный стабилизатор напряжения | |

|

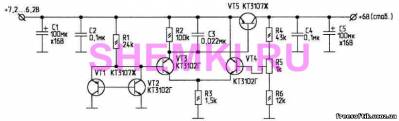

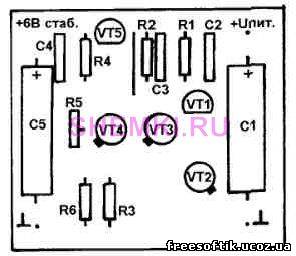

Автор разработки: О.Белоусов Схема принципиальная Экономичный стабилизатор напряженияПредлагаемая схема стабилизатора (рис.1) имеет высокий КПД — порядка 93% (при токе нагрузки 20 мА) и потребляемый ток — всего 0,7 мА. Это достигается тем, что стабилизатор построен по схеме "с малым напряжением потерь", и в качестве элемента стабилизации применен аналог низковольтного стабилитрона. Минимальный ток стабилизации, по утверждению автора - «Аналоги низковольтных стабилитронов - схемы, описания, справочные материалы», составляет 0,1 мА.   Похожие материалы: | |

|

| |